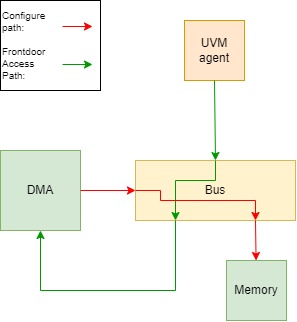

In UVM there are two ways of connecting the register model to UVM agents that operate on the design under test. One is using the register adapter, uvm_reg_adapter. What that class does is to convert from a register model sequence item to a sequence item that can be used by our UVM agent’s sequencer. That works well if there is a one-to-one relationship between the register access and the transactions of the UVM agent. When we need a more complex use of the UVM agent to facilitate the register access, the register adapter falls short. This might be in cases when the source of the register access is not the UVM agent we are using, but it originates from somewhere inside the design under test which we only have indirect access to. Think about a DMA inside a larger system, where we use the UVM agent to configure the DMA to do the access we want. To do this we would need to map the register access to a series of transactions from the UVM agent. In those cases, the UVM register frontdoor sequence, uvm_reg_frontdoor, is the king.

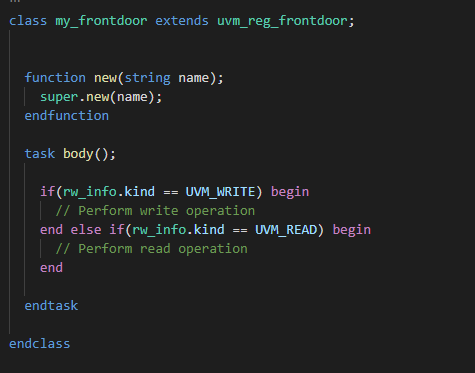

The uvm_register_frontdoor looks like a normal uvm_sequence apart from having the uvm_reg_item rw_info that holds information about the register access. Like if the access is read or write, what the address offset of the access is and a handle to the reqister or memory the access was made to.

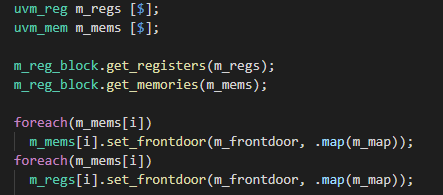

In the picture above you will see how recognizable the uvm_reg_frontood sequence is, with the body task where the work is done. This is where you will assemble the sequence items and send them to the driver using the send_request function. You also see that in my example the kind variable of the rw_info element is used to decide whether the transaction is a read transaction or not. What is next is that we need to connect the frontdoor sequence to the register model and to the sequencer of the UVM agent it is using. As opposed to the register adapter there is not any shortcut to connect the front door to all memories and registers in the register model. So, the user have to do it manually. I recommend this method for doing it:

Connecting it to the sequencer can simply be done by running set_sequencer on the map you want the register map to be frontdoor to be associated with. Like this:

Leave a reply to Carter Cancel reply